# π Type 구조를 이용한 Harmonic suppression 및 Wilkinson divider의 소형화 설계

선은정\*. 김정현

\*한양대학교 전자공학과

\*alal8000@hanyang.ac.kr, junhkim@hanyang.ac.kr

# Design of Harmonic Suppression and Miniaturized Wilkinson divider using $\pi$ Type Structure

Seon Eun Jung\*, Kim Jung Hyun

\*Department of Electrical and Electronic Engineering Hanyang Univ.

### 요 약

본 논문은 capacitive loading을 통해 conventional wilkinson power divider의 layout size를 감소시키며 harmonic을 억제하는 wilkinson power divider를 설계하였다. 설계된 divider는 center frequency 0.8 GHz frequency에서 0.29 dB의 Insertion Loss (IL)를 가지며, 5<sup>th</sup> harmonic frequency까지 harmonic suppression이 효과적으로 나타남을 simulation을 통해 확인하였다.

#### I. 서 론

Wilkinson power divider와 combiner는 power amplifier와 구성하여 쓰기에 매우 중요한 component이다. Conventional wilkinson divider는 구조가 간단하여 비교적 설계가 용이하지만, wilkinson power divider의 quarter-wave line의 physical length로 인해 circuit의 layout size가 증가하게 된다. 이는 추후 cost의 증가로 이어지므로 wilkinson power divider의 size를 줄이면서 harmonic을 억제하는 설계를 진행하였다.

본 논문에서는 conventional wilkinson power divider의 quarter-wave line을 사용하지 않고 capacitive loading을 통해 layout size를 최적화 하는 설계를 제안한다. Quarter-wave line 구조를 open stub와 45 degree의 electrical length를 가진 line의 π 구조로 대체하여 구성하였다. 이때 center frequency는 0.8 GHz이다.

## Ⅱ. 본론

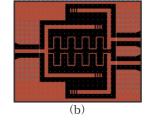

Fig.1은 제안된 capacitive loading  $\pi$  구조인 wilkinson divider의 schematic과 layout을 보여준다. 제안된 wilkinson divider는 FR4 dielectric substrate (constant = 4.2, height = 400 um) 기판으로 설계하였다. 이때  $\pi$  구조 line의 electrical length는 quarter—wave line의 절반인 45 degree로 하여 전체 layout의 크기를 줄일 수 있게 하였다. Pad를 포함한 전체 layout의 폭과 길이는  $27 \times 21$  때 이며 conventional wilkinson divider의 layout ( $41 \times 18$  때)과 비교하였을 때 24 %의 면적 감소를 확인하였다.

The state of the s

Fig.1. 제안된 Wilkinson power divider

(a) Schematic (b) Layout

#### Ⅲ. 결론

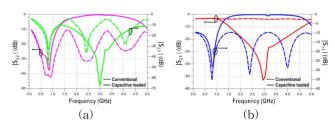

Fig.2는 제안된 wilkinson power divider와 coventional wilkinson power divider의 s-parameter의 비교를 나타낸다. S<sub>11</sub>의 경우 두 divider 모두 0.8 GHz에서 -27 dB 미만의 결과를 보이며 S<sub>22</sub>, S<sub>33</sub>의 경우 역시 두 divider 모두 -36 dB 미만으로 확보되어 모든 port에서 matching 되었음을 확인하였다. S<sub>23</sub>는 0.8 GHz에서 두 경우 모두 -40 dB 미만으로 output port 간의 isolation을 충분히 확보하였다. Conventional divider의 경우 0.8 GHz에서의 IL이 0.18 dB, 제안된 divider의 IL은 0.29 dB로 제안된 divider의 IL이 약 0.1 dB 낮은 차이를 보이지만 conventional 구조와 비교하여 제안된 divider의 S<sub>21</sub>이 high order harmonic frequency에서 -11 dB 미만임을 통해 harmonic 억제를 효과적으로 이루었음을 확인하였다.

Fig.2. Conventional divider와 제안된 divider의 s-parameter 비교 plot

(a)  $S_{21}$  and  $S_{11}$  (b)  $S_{22}$  and  $S_{23}$

### ACKNOWLEDGMENT

본 연구는 IDEC에서 EDA Tool를 지원받아 수행하였습니다. 이 논문은 2023년도 과학기술정보통신부 (과학기술사업화진흥원) 정부 재원으로 2023년 지역산업연계 대학 Open-Lab 육성지원사업의 지원을 받아 수행

## 참고문헌

- [1] M. C. Scardelletti, G. E. Poncchak, and T. M. Weller "Miniaturized Wilkinson Power Dividers Utilizing Capacitive Loading" IEEE Microwave and Wireless Components Letters. vol. 12, no. 1, January. 2002.

- [2] Xiaolong Wang. Zhewang Ma, Iwata Sakagami "A Compact and Harmonic Suppression Wilkinson Power Divider with General  $\pi$  Type Structure" IEEE MTT-S International Microwave Symposium, 2015